Bootstrap Paginator 分页插件

本文共 685 字,大约阅读时间需要 2 分钟。

一、插件简介

Bootstrap Paginator是一款基于Bootstrap和jQuery的分页组件。

github地址为:

中文介绍比较详细的:

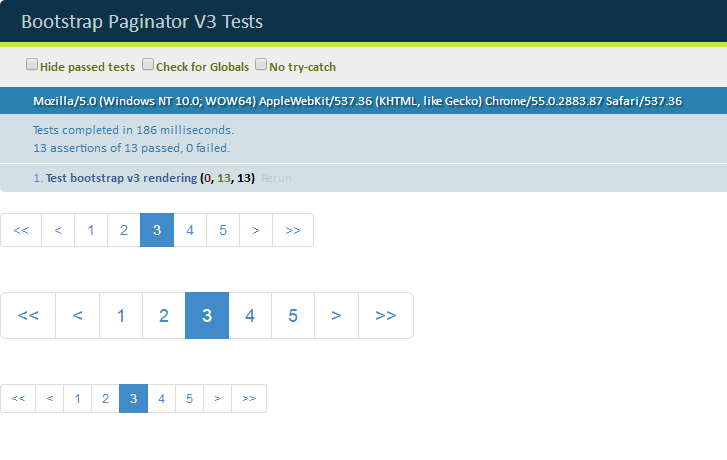

效果图如下:

二、插件使用

1、下载源码

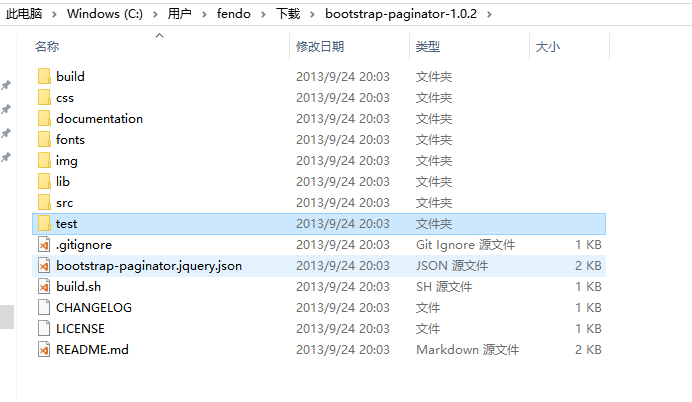

下载最新的源码解压之后,如下:

2、引入必要的css和js文件。

3、用一个div来展示

4、JS代码

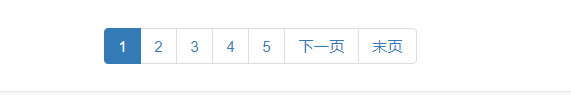

$('#pageLimit').bootstrapPaginator({ currentPage: 1, totalPages: 10, size:"normal", bootstrapMajorVersion: 3, alignment:"right", numberOfPages:5, itemTexts: function (type, page, current) { switch (type) { case "first": return "首页"; case "prev": return "上一页"; case "next": return "下一页"; case "last": return "末页"; case "page": return page; } }}); 5、效果如下

你可能感兴趣的文章

mysql

查看>>

MTK Android 如何获取系统权限

查看>>

MySQL - 4种基本索引、聚簇索引和非聚索引、索引失效情况、SQL 优化

查看>>

MySQL - ERROR 1406

查看>>

mysql - 视图

查看>>

MySQL - 解读MySQL事务与锁机制

查看>>

MTTR、MTBF、MTTF的大白话理解

查看>>

mt_rand

查看>>

mysql -存储过程

查看>>

mysql /*! 50100 ... */ 条件编译

查看>>

mudbox卸载/完美解决安装失败/如何彻底卸载清除干净mudbox各种残留注册表和文件的方法...

查看>>

mysql 1264_关于mysql 出现 1264 Out of range value for column 错误的解决办法

查看>>

mysql 1593_Linux高可用(HA)之MySQL主从复制中出现1593错误码的低级错误

查看>>

mysql 5.6 修改端口_mysql5.6.24怎么修改端口号

查看>>

MySQL 8.0 恢复孤立文件每表ibd文件

查看>>

MySQL 8.0开始Group by不再排序

查看>>

mysql ansi nulls_SET ANSI_NULLS ON SET QUOTED_IDENTIFIER ON 什么意思

查看>>

multi swiper bug solution

查看>>

MySQL Binlog 日志监听与 Spring 集成实战

查看>>

MySQL binlog三种模式

查看>>